이 보고서는 코스닥 기업에 대한 투자정보 확충을 위해 발간한 보고서입니다.

기술분석보고서

YouTube 요약 영상 보러가기

# 시그네틱스(033170)

## 반도체/반도체장비

요약

기업현황

시장동향

기술분석

재무분석

주요 변동사항 및 전망

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |       |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|-----------|

| 작성 기관                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NICE평가정보(주) | 작 성 자 | 조상진 선임연구원 |

| <p>■ 본 보고서는 「코스닥 시장 활성화를 통한 자본시장 혁신방안」의 일환으로 코스닥 기업에 대한 투자정보 확충을 위해, 한국거래소와 한국예탁결제원의 후원을 받아 한국IR협의회가 기술신용평가기관에 발주하여 작성한 것입니다.</p> <p>■ 본 보고서는 투자 의사결정을 위한 참고용으로만 제공되는 것이므로, 투자자 자신의 판단과 책임하에 종목선택이나 투자시기에 대한 최종 결정을 하시기 바랍니다. 따라서 본 보고서를 활용한 어떠한 의사결정에 대해서도 본회와 작성기관은 일체의 책임을 지지 않습니다.</p> <p>■ 본 보고서의 요약영상은 유튜브로도 시청 가능하며, 영상편집 일정에 따라 현재 시점에서 미리보기 상태일 수 있습니다.</p> <p>■ 카카오톡에서 “한국IR협의회” 채널을 추가하시면 매주 보고서 발간 소식을 안내 받으실 수 있습니다.</p> <p>■ 본 보고서에 대한 자세한 문의는 작성기관(TEL.02-2124-6822)으로 연락주시기 바랍니다.</p> |             |       |           |

한국IR협의회

# 시그네틱스(033170)

국내 최초 반도체 어셈블리 및 테스트 전문기업

## 기업정보(2021/01/01 기준)

|      |                                  |

|------|----------------------------------|

| 대표자  | 김재홍                              |

| 설립일자 | 1966년 09월 12일                    |

| 상장일자 | 2010년 11월 26일                    |

| 기업규모 | 중견기업                             |

| 업종분류 | 반도체패키징                           |

| 주요제품 | 라미네이트패키지/<br>플립칩패키지/리드<br>프레임패키지 |

## 시세정보(2021/03/09 기준)

|            |            |

|------------|------------|

| 현재가(원)     | 1,350      |

| 액면가(원)     | 500        |

| 시가총액(억 원)  | 1,157      |

| 발행주식수      | 85,728,319 |

| 52주 최고가(원) | 1,940      |

| 52주 최저가(원) | 410        |

| 외국인지분율     | 2.19%      |

| 주요주주       | (주)영풍      |

## ■ 글로벌 TOP 반도체 후공정 및 테스트 사업을 영위하는 전문기업

시그네틱스는 1966년에 반도체 제조를 시작한 국내 반도체 어셈블리 및 테스트 전문기업이다. 우수한 반도체 패키징 및 성능검사 기술로 세계 굴지의 전자회사를 대상으로 전자 부품용 각종 반도체를 공급하는 기업으로 제품별 고객사 요구와 반도체 시장 상황에 맞는 특성화된 제품을 적기에 개발하여 공급하고 있으며, 제품 성능과 요구사항에 따라 높은 신뢰성 수준과 열적/전기적으로 우수한 패키지 제품을 개발하고 있다. 시그네틱스는 세계 반도체 패키지 시장에서 요구하는 플립칩(FlipChip), Thermal Enhanced BGA(Ball Grid Array), FBGA(Fine Pitch BGA), MCM (Multi-Chip Modules) 등의 최첨단 패키지 기술을 보유하고 있으며, 지속적인 연구 개발 및 설비투자를 통해 기술경쟁력을 유지하고 있다.

## ■ 지문인식 센서 패키지 기술확보를 통한 시장 개척

지문인식 센서 패키지 기술을 개발하여 매출을 확대하였고, 고부가가치 프리미엄 반도체 패키징 타입인 Recon 플립칩을 개발하여 양산 중에 있다. 최근에는 전자기기들의 경량화, 다기능화에 따른 반도체 패키지의 새로운 비즈니스 매출창출을 위한 LAB(Laser Assisted Bond System) 기술을 투자 및 개발 중에 있다. 또한, Advanced SiP(System In-Package) Module 제품의 수요 증가로 개발 및 초도 양산 인프라를 확보하였다.

## ■ IoT, 자율주행 자동차, 인공지능 반도체 등의 차세대 시스템 반도체를 위한 특화된 첨단 패키지의 기술개발 및 투자를 통한 신시장 진출

4차 산업혁명이 일어나면서 IoT, 자율주행 자동차, 인공지능 반도체 등의 차세대 시스템 반도체에 대한 수요가 증가하고 있으며, 세계 반도체 선도기업들이 다투어 개발하고 있다. 이에 차세대 시스템 반도체에 특화된 패키지 기술을 개발하여 기술경쟁력을 확보하고 새로운 시장에 대한 개척을 공격적으로 모색하고 있다.

## 요약 투자지표 (K-IFRS 연결 기준)

| 구분<br>년 | 매출액<br>(억 원) | 증감<br>(%) | 영업이익<br>(억 원) | 이익률<br>(%) | 순이익<br>(억 원) | 이익률<br>(%) | ROE<br>(%) | ROA<br>(%) | 부채비율<br>(%) | EPS<br>(원) | BPS<br>(원) | PER<br>(배) | PBR<br>(배) |

|---------|--------------|-----------|---------------|------------|--------------|------------|------------|------------|-------------|------------|------------|------------|------------|

| 2017    | 2,656        | 23.2      | 28            | 1.0        | 16           | 0.6        | 1.0        | 0.7        | 39.3        | 19         | 1,956      | 69.8       | 0.7        |

| 2018    | 2,502        | (5.8)     | (72)          | (2.9)      | (62)         | (2.5)      | (4.0)      | (2.9)      | 36.0        | (73)       | 1,719      | (11.9)     | 0.5        |

| 2019    | 2,188        | (12.6)    | (196)         | (8.9)      | (200)        | (9.1)      | (13.9)     | (10.3)     | 33.3        | (233)      | 1,627      | (4.9)      | 0.7        |

## 기업경쟁력

### 생산체계 전략

#### ■ Fine Pitch Wire Bonder 구비

- 고성능 및 Fine Pitch에 적합한 Iconn 등의 Wire Bonder 설비를 교체하여 시장변화에 대응

#### ■ 12인치 wafer 생산 가능한 설비 구축

- Back Grinding, Die Bonder 등 12인치 wafer를 생산할 수 있는 설비를 구축

## 핵심기술 및 적용제품

### 핵심기술

#### ■ 플립칩 패키지 기술

#### ■ Thermal Enhanced BGA 기술

#### ■ Fine Pitch BGA 기술

#### ■ Multi-Chip Module 기술

## 지문인식 센서 전용 패키지 개발

### ■ 지문인식 센서용 반도체 패키지 기술개발

### ■ 기술장벽 구축을 위한 지재권 확보

### ■ 지문인식 센서 패키징 기술을 통한 신규 고객 확대

## 주요제품

### ■ 라미네이트 패키지, 플립칩 패키지, 리드프레임 패키지

라미네이트 패키지

플립칩 패키지

리드프레임 패키지

## 시장경쟁력

### 시장의 확대

#### ■ 4차 산업 혁명에 의한 시스템 반도체 시장확대

- IoT, 자율주행 자동차, 인공지능 반도체 분야로 시장확대

- 차세대 시스템 반도체에서 매출 확대 기대

## 최근 변동사항

### 신규 패키지 기술개발

#### ■ 고부가가치 프리미엄 반도체 패키지인

Recon 플립칩을 개발 및 지속 투자하여 양산 중임.

#### ■ 다기능화 경향에 따른 Advanced SIP Module 양산

## 국내 반도체 패키징 시장현황

| 년도    | 시장 규모      | 성장률                        |

|-------|------------|----------------------------|

| 2019년 | 183,091억 원 | 연평균 4.87% ▲<br>(Technavio) |

| 2021년 | 201,463억 원 |                            |

## 첨단 생산체제 구축

### ■ Fine Pitch Filp Chip Bonder 구비

### ■ 12인치 wafer 생산 가능한 설비 구축

## I. 기업 현황

### 글로벌 TOP 반도체 후공정 및 테스트 사업을 영위하는 전문기업

시그네틱스는 우수한 반도체 패키징 및 성능검사 기술로 세계 굴지의 전자회사를 대상으로 전자 부품용 각종 반도체를 공급하는 종합 반도체 패키지 전문기업이다.

#### ■ 개요

시그네틱스(이하 ‘동사’ )는 비메모리 첨단기술로 글로벌 TOP 반도체 후공정 및 테스트 사업을 영위하는 전문기업이다. 전자장치 및 동 부속품의 제작과 판매 등을 목적으로 1966년 미국 Signetics Corporation의 전액 투자로 외자도입법에 따른 외국인투자기업으로 설립 등록 되었다. 2000년 4월에 (주)영풍이 인수하였고 2010년 11월 26일 코스닥시장에 상장되었으며, 국내외 유수 전자업체와 긴밀하고 장기적인 협력 관계를 유지하여 선도적인 반도체 공급업체로 자리매김하였다. 현재 세계 반도체 패키징 시장에서 요구하는 플립칩, Thermal Enhanced BGA, FBGA, MCM 등 시장 상황에 맞는 특성화된 제품을 적기에 개발하여 제공하고 있으며, 제품의 성능과 요구사항에 따라 높은 신뢰성 수준과 열적/전기적으로 우수한 반도체 패키지를 개발하고 제조함으로써 반도체 패키징 전문기업으로 지속적인 성장을 하고 있다.

표 1. 기업현황

| 구분      | 내용                               | 구분    | 내용                                                                 |

|---------|----------------------------------|-------|--------------------------------------------------------------------|

| 회사명     | 시그네틱스(주)                         | 최대주주  | (주)영풍                                                              |

| 설립일     | 1966년 9월 12일                     | 대표이사  | 김재홍                                                                |

| 자본금     | 429억 원 (2016년 기준)                | 임직원 수 | 140명 (2020년 09월 30일 기준)                                            |

| 발행주식 총수 | 85,728,319주<br>(2020년 9월 30일 기준) | 주요고객  | 삼성전자, LG전자, SK하이닉스, 브로드컴, 애플, IDT, 소니, 후지츠 NEC 등 국내외 60개 이상 고객사 확보 |

| 상장일     | 2010년 11월 26일 (코스닥)              | 주요제품  | 라미네이트 패키지, 플립칩 패키지, 리드프레임 패키지                                      |

| 지식재산권   | 국내 건, 해외 건                       |       |                                                                    |

\*출처: 분기보고서(2020), NICE평가정보(주) 재구성

#### ■주요주주

2000년도에 (주)영풍이 지배기업의 지분 79.88%를 인수함으로써 독점규제 및 공정거래에 관한 법률에서 규정하는 대규모 기업집단으로 2000년 6월 지정되었으며, 2010년 11월 26일에 주식을 한국거래소(코스닥시장)에 상장하였다. 현재 동사의 최대주주는 (주)영풍으로 31.62%의 지분을 가지고 있다.

**표 2. 주요주주**

| 주요주주      | 주식수        | 지분율(%) |

|-----------|------------|--------|

| 주식회사 영풍   | 27,106,230 | 31.62  |

| 영풍전자 주식회사 | 1,668,989  | 1.95   |

| 장형진       | 7,585,746  | 8.85   |

| 기타        | 49,367,354 | 57.58  |

| 합계        | 85,728,319 | 100    |

\*출처: 분기보고서(2020), NICE평가정보(주) 재구성

## ■ 대표이사 정보

김재홍 대표이사는 숭실대학교 전자공학과를 졸업하고 제일모직 전자재료 구미사업장 공장장, 삼성 SDI 전자재료 사업팀 부사장 및 자문역을 역임하였으며, 2018년 3월부터 동사의 대표이사로 안정적으로 경영하고 있다.

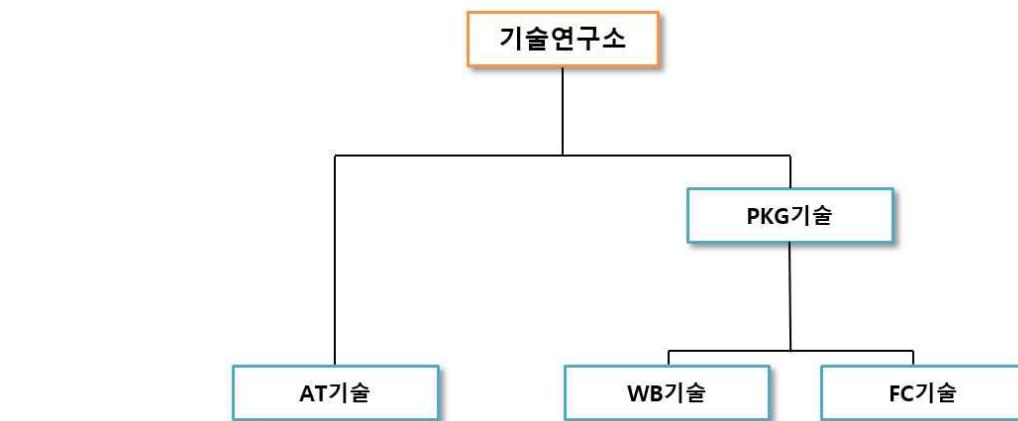

## ■ 조직 구성

동사의 기술연구소 조직은 패키지(PKG) 기술개발을 위해 WB 기술팀과 FC 기술팀 등으로 구성하고 있으며, ISO 9001, IATF16949, ISO 14001, ISO 45001, SAMSUNG ECO Partner 등 품질인증을 획득하여 신뢰할 수 있는 제품을 생산하고 있다.

**그림 1. 기술연구소 조직 구성도**

\*출처: 분기보고서(2020), NICE평가정보(주) 재구성

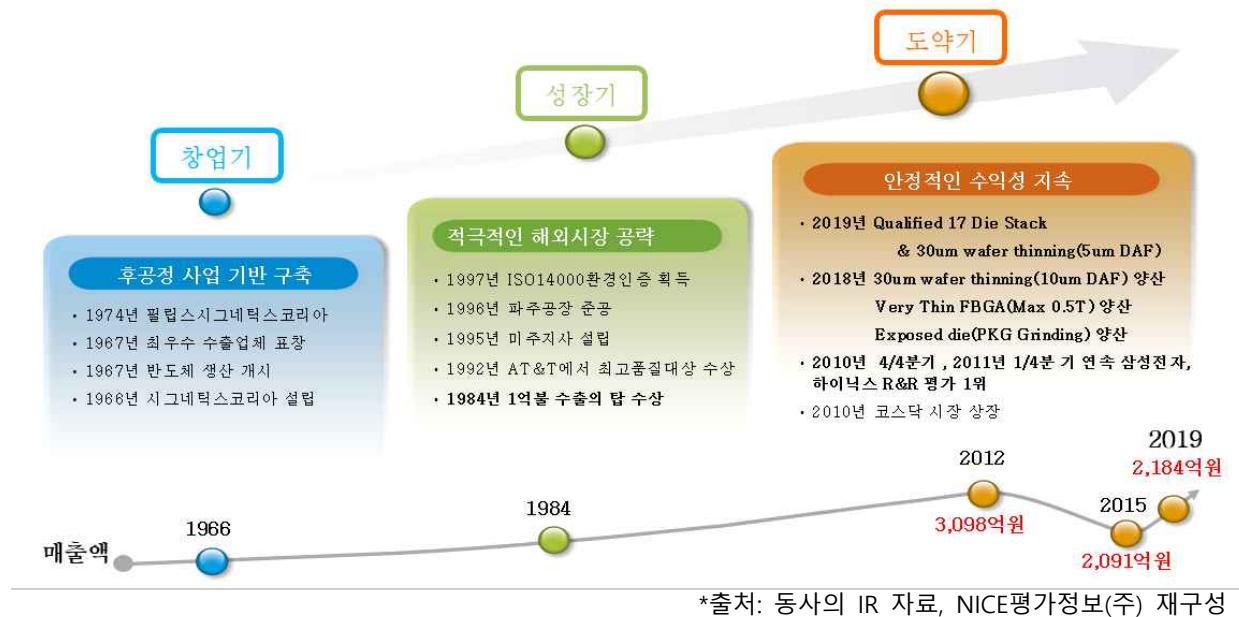

## ■ 성장 연혁

후공정 사업의 기반을 구축한 창업기, 적극적인 해외시장을 공략한 성장기를 거쳐 영풍그룹에 편입된 후 안정적인 수익성을 지속하며 도약기를 맞고 있다. 2010년 코스닥에 상장되었으며, 2010년 4/4분기, 2011년 1/4분기 연속 삼성전자, SK하이닉스 R&R 평가 1위를 차지하였다. 2015년에는 동사의 미국법인을 설립하여 글로벌 IDM(Integrated Device Manufacturer) 반도체 기업을 대상으로 한 마케팅 확대로 지속적인 해외경쟁력을 강화하며 해외시장 점유율을 넓히고 있다.

그림 2. 성장 연혁

## ■ 반도체 패키지 시장점유율

패키징 전문업체는 세계적으로 약 150여 개 업체가 있고, 주요 업체인 ASE, 앰코테크놀로지, SPIL, 스태츠칩팩을 중심으로, 상위 4개 업체가 시장의 46%를 차지하는 과점체제가 구축되어 있다. 동사는 국내 반도체 패키지 시장에서 6.6%의 점유율을 차지하고 있으며, 세계 시장 점유율은 대략 0.3%를 차지하고 있다.

표 3. 국내 반도체 패키지 시장점유율

| 2019년    | 시그네틱스 | 하나마이크론 | SFA반도체 | 앰코테크놀로지<br>코리아 | ASE<br>코리아 | 에이티세미콘 | 원팩  |

|----------|-------|--------|--------|----------------|------------|--------|-----|

| 매출액(억 원) | 2,185 | 2,987  | 4,618  | 16,889         | 4,868      | 1,259  | 206 |

| 시장점유율(%) | 6.6   | 9      | 14     | 51.2           | 14.7       | 3.8    | 0.6 |

\*출처: 분기보고서(2020), NICE평가정보(주) 재구성

## ■ 주요제품

동사의 사업은 크게 메모리와 비메모리 반도체 제조로 구분할 수 있으며 67%의 매출이 비메모리 반도체에서 나오고 있다. 주요제품에는 라미네이트 패키지, 플립칩 패키지, 리드프레임 패키지 등이 있다.

표 4. 주요제품 매출 (2020년 3분기)

| 사업 구분     | 매출 유형 | 품목   | 구제적 용도            | 주요매출처  | 매출액(백만원) | 비중(%)  |

|-----------|-------|------|-------------------|--------|----------|--------|

| 반도체<br>제조 | 제품    | 메모리  | PC 주변장치 및<br>저장장치 | 삼성전자 외 | 46,408   | 33.11% |

|           |       | 비메모리 | 통신장비, PC 등        | 브로드컴 외 | 93,755   | 66.89% |

| 합계        |       |      |                   |        | 140,163  | 100%   |

\*출처: 분기보고서(2020), NICE평가정보(주) 재구성

표 5. 패키지 주요 제품 사진

| 종류           | 제품명 및 사진 |          |         |

|--------------|----------|----------|---------|

|              | FBGA     | (HS)PBGA | MAP BGA |

| 라미네이트<br>패키지 |          |          |         |

| 플립칩<br>패키지   |          |          |         |

|              |          |          |         |

| 리드프레임<br>패키지 |          |          |         |

| VG(D)FN      |          |          |         |

\*출처: 회사 홈페이지, NICE평가정보(주) 재구성

## ■ 신규사업 및 전망

동사는 지문인식 센서 패키지 기술개발을 통하여 매출을 확대하였고, 고부가가치 프리미엄 반도체 패키지인 Recon 플립칩을 개발 및 지속 투자하여 양산하고 있다. 최근에는 전자기기들의 경량화, 다기능화에 따른 반도체 패키지의 SIP, Large Body, Fine Pitch 등 새로운 비즈니스 매출창출을 위한 LAB 기술을 투자 및 개발하고 있다. 또한, Advanced SIP Module 제품의 수요 증가로 개발 및 초도 양산 인프라를 확보하였다.

## II. 시장 동향

### 4차 산업혁명 시대 핵심인 시스템 반도체 시장과 국내 반도체 패키지 시장

시그네틱스는 비메모리 첨단기술인 반도체 패키징 및 성능검사 기술로 세계 전자회사를 대상으로 전자 부품용 각종 반도체를 공급하는 종합 반도체 패키지 전문기업으로 비메모리 반도체 및 반도체 패키지 산업에 대한 시장 동향을 조사하였다.

#### ■ 반도체 산업 현황

##### ▶▶ 반도체 산업의 구분 및 특성

반도체 산업은 크게 반도체 소자제조업, 반도체 장비 및 원·부자재 제조업 등을 모두 포함하며, 반도체 산업의 인프라를 구성하는 기초·기반기술, 지식산업으로 구분할 수 있다. 좁은 의미의 반도체 산업은 설계, wafer 가공, 조립 및 테스트 사업 부문으로 나눌 수 있다. 반도체 기업은 설계 및 제조를 모두 하는 IDM, 에셈블리 및 테스트를 하는 패키징 업체, 반도체 위탁생산 제조 전문업체인 파운드리(Foundry), 반도체 설계 전문업체인 팹리스(Fabless)로 구분할 수 있다. 대표적인 IDM 기업은 삼성전자, 인텔, SK하이닉스 등이고, 팹리스 회사는 퀄컴, 브로드컴, 미디어텍 등이 있으며, 동사의 사업이 포함되고 있는 패키징(Packaging) 회사는 시그네틱스, 앰코테크놀로지, ASE, SFA반도체 등이 있다.

표 6. 반도체 산업의 구분 및 특징

| 구분                 | 특징                                                                                                                 | 주요 업체                                  |

|--------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 종합 반도체 업체<br>(IDM) | <ul style="list-style-type: none"><li>- 기획, R&amp;D, 설계, 생산, 판매 등을 일괄 수행</li><li>- 대규모 R&amp;D 및 설비투자 필요</li></ul> | 삼성전자, 인텔, SK하이닉스 등                     |

| 패키징<br>(Packaging) | <ul style="list-style-type: none"><li>- 가공된 wafer의 어셈블리 및 테스트 전문회사</li><li>- 축적된 경험 및 거래선 확보 필요</li></ul>          | 시그네틱스, 앰코테크놀로지, ASE, SFA반도체 등          |

| 파운드리<br>(Foundry)  | <ul style="list-style-type: none"><li>- wafer의 가공만을 전문적으로 수행</li><li>- 전문 수탁 생산회사 (고부가 비메모리 위주)</li></ul>          | TSMC, UMC, 동부하이텍, SMIC 등               |

| 팹리스<br>(Fabless)   | <ul style="list-style-type: none"><li>- 설계 기술만 보유하고 위탁생산 판매</li><li>- 높은 기술, 인력 인프라 요구</li></ul>                   | 퀄컴, 브로드컴, 미디어텍, 실리콘마이터스, 실리콘웍스, 엠텍비전 등 |

\*출처: 분기보고서(2020), NICE평가정보(주) 재구성

또한, 반도체는 크게 시스템 반도체와 메모리 반도체로 구분할 수 있다. 메모리는 표준품의 대량생산에 필요한 생산기술이 요구되며, 비메모리는 시스템의 운용에 필요한 설계 기술이 경쟁력의 핵심이다. 한편, 비메모리 반도체는 대부분 활용 분야가 다양하여 공급이 급격히 증가하더라도 수요 측면에서 이를 흡수할 수 있지만, 메모리 반도체는 수요가 특정 기기에 한정되어 있어 공급 급증이 수급 불균형을 초래할 수 있다.

표 7. 메모리 반도체와 시스템 반도체의 사업 비교

| 구분     | 메모리 반도체     | 비메모리 반도체(시스템 반도체) |

|--------|-------------|-------------------|

| 용도     | 정보 저장       | 정보처리              |

| 제품     | D램, 낸드플래시 등 | CPU, AP, 센서 등     |

| 생산방식   | 소품종 대량생산    | 다품종 소량생산          |

| 산업 특징  | 대규모 설비투자 필요 | 설계인력 중심 기술 집약     |

| 가격 변동성 | 수요 변화에 민감   | 수요 변화에도 안정적       |

\*출처: 산업연구원자료, NICE평가정보(주) 재구성

반도체 시장의 2/3를 차지하는 비메모리 반도체 수요가 크게 성장함에 따라 반도체 패키징 산업도 반도체 산업 전반과 맥락을 같이하여 삼성전자, SK하이닉스 등에서 제조되는 wafer를 최종 사용자의 요구 규격에 맞도록 조립과 테스트를 해야 하는 필연적인 관계를 맺고 있다. 국내 주요 패키징 업체인 시그네틱스, 엠코테크놀로지코리아, ASE코리아, 하나마이크론, SFA반도체 등은 반도체 소자 업체와의 유기적인 관계를 유지하며 신 패키지 개발에 동참하고 있다.

현재까지 반도체 기술은 나노미터의 선풍, 백만 개 이상의 셀, 고속, 많은 열 방출 등으로 발달하고 있으나 상대적으로 패키징 기술은 낙후되어 있어 반도체의 전기적 성능이 반도체 자체의 성능보다는 패키징과 이에 따른 전기 접속으로 결정되고 있다. 실제로 고속 전자제품의 전체 전기신호 지연은 50% 이상이 칩과 칩 사이에서 발생하는 패키지 지연 때문에 발생하며 이는 향후 시스템의 크기가 큰 경우, 80% 이상으로 예상되어 패키징 기술의 중요성이 더욱 커지고 있다.

### ▶▶ 반도체 시장 규모

세계반도체무역통계기구(World Semiconductor Trade Statistics)는 2020년의 반도체 시장 규모가 작년보다 3.3% 증가한 4,259억 달러를 기록할 것으로 전망하였다. WSTS는 지난해 12월 올해 세계 반도체 시장이 전년 대비 5.9% 성장할 것으로 전망했지만, Covid-19에 따른 영향으로 전망치를 하향 조정하였다.

표 8. 세계반도체무역통계기구의 반도체 시장 규모 전망치

| 구분                         | 매출액(억 달러) |      |      | 성장률(%) |      |      |

|----------------------------|-----------|------|------|--------|------|------|

|                            | 2019      | 2020 | 2021 | 2019   | 2020 | 2021 |

| 전체 반도체 시장                  | 4112      | 4259 | 4522 | -12    | 3.3  | 6.2  |

| 메모리 반도체                    | 1064      | 1224 | 1360 | -32.6  | 15   | 11.2 |

| 비메모리 반도체                   | 3048      | 3035 | 3162 | -1.5   | -0.4 | 4.2  |

| - 아날로그 IC                  | 539       | 508  | 538  | -8.2   | -5.8 | 5.9  |

| - 마이크로컴포넌트                 | 664       | 681  | 691  | -1.2   | 2.6  | 1.4  |

| - 로직 IC                    | 1065      | 1097 | 1140 | -2.5   | 2.9  | 3.9  |

| - 개별소자(Discrete Component) | 229       | 223  | 236  | -0.9   | -6.6 | 5.7  |

| - Optoelectronics          | 416       | 394  | 419  | 9.3    | -5.1 | 6.1  |

| - Sensors                  | 135       | 132  | 138  | 1.2    | -2.1 | 4.6  |

\*출처: WSTS(2020), NICE평가정보(주) 재구성

2020년 기준으로 메모리 반도체 시장 규모는 1,224억 달러이고 비메모리 반도체 시장 규모는 약 3,035억 달러로 비메모리 반도체 시장이 메모리 반도체 시장보다 대략 2.5배 크다. 전체 시장 전망치는 하향됐지만, 메모리는 오히려 매출이 큰 폭 늘어날 것으로 상향 조정됐다. 2020년 메모리 시장이 1,224억 달러 규모를 형성해 작년 대비 15% 확대될 것으로 전망된다. 스마트폰 수요 하락은 서버 메모리 수요 상승으로 상쇄됐고, 생산 업체 투자 축소로 공급 증가량은 억제돼 이 같은 전망이 나온 것으로 분석된다. 비메모리 반도체의 경우는 2020년에 0.4% 감소한 3,035억 달러로 전망되며, 2021년에는 3,162억 달러로 성장할 것으로 예상된다.

그림 3. Covid-19에 의한 글로벌 IC시장 전망치 영향

IC 인사이트에 의하면, 글로벌 IC 시장 전망치가 3월 기준으로 3% 성장이었으나, 4월에는 4% 감소할 것으로 예측치가 수정되었다. Covid-19 팬데믹으로 인해 성장률이 급격하게 감소할 것으로 예상된다.

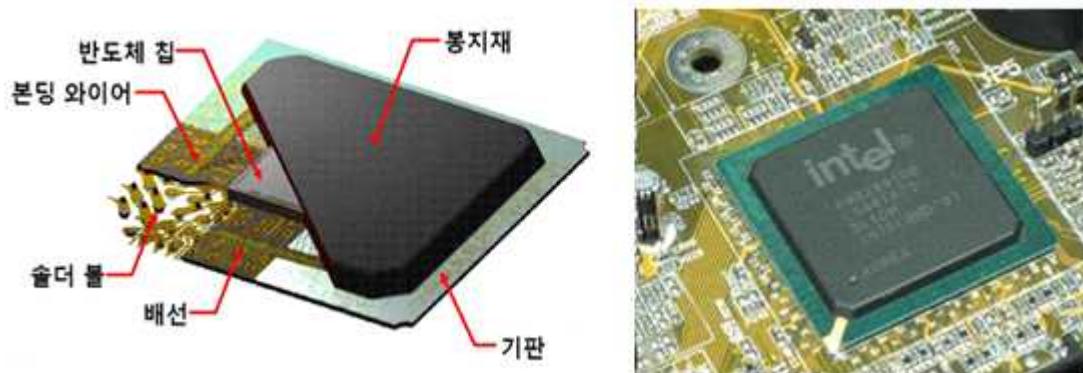

## ▶▶ 반도체 패키징 시장

반도체 패키지는 미세 전기회로가 집적된 반도체 칩을 외부 영향으로부터 보호할 수 있도록 밀봉하여 포장하는 동시에 외부와의 전기적 연결 및 열 방출 경로를 확보하여 완제품화한 것으로 이를 제작하는 공정이 패키징이다.

반도체 제품은 반드시 패키징 공정을 통해 외부로부터 보호가 가능한 형태로 출하되어야 하므로, 패키징은 내부의 집적회로와 함께 최종적인 제품 성능을 결정하는 반도체 기술의 핵심적인 요소이다. 최근의 반도체 제품은 점차 고속화 및 소형화되고 있으므로 이에 대응하는 패키지 역시 미세집적 기술을 통해 패키지에 의한 동작 속도 저하와 추가적인 부피 증가를 최소화하는 방향으로 발전하고 있다.

한편, 반도체 패키징 산업의 특징은 진입장벽이 높은 산업, 반도체 업황에 민감한 산업, 주문 제작 산업, 지식 기반 고부가가치 산업 등으로 요약된다. 반도체 패키징 및 조립 장비산업의 벨루 체인은 전자, 기계, 광학 부품 → 반도체 패키징 및 조립 장비 → 반도체 제조 등으로 구성된다.

**그림 4. 반도체 패키지: (좌) 단면도 (우) 메인보드에 실장된 반도체 패키지**

\*출처: Chip-package system workshops, SemiWiki.com(2012) NICE평가정보(주) 재구성

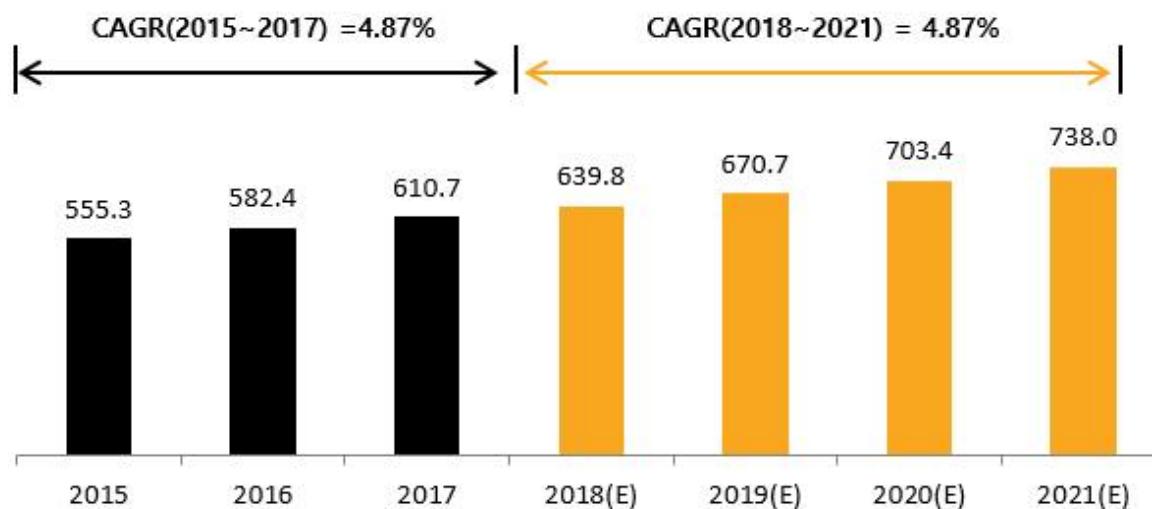

2018년 발간된 Technavio 자료에 따르면, 세계 반도체 패키징 시장은 2017년 610억 7천만 달러 규모이며, 이후 연평균 4.87%씩 증가하여 2022년에는 774억 5천만 달러에 달할 것으로 전망된다. 세계 반도체 패키징 및 조립 장비 시장은 홍콩의 ASM Pacific Technology, 싱가포르의 Kulicke & Soffa와 Besi, 일본의 Tokyo Seimitsu, Disco, Tokyo Electron 등이 선도하고 있다.

**그림 5. 세계 반도체 패키징 시장 규모(단위: 억 달러)**

\*출처: Technavio(2018), NICE평가정보(주) 재구성

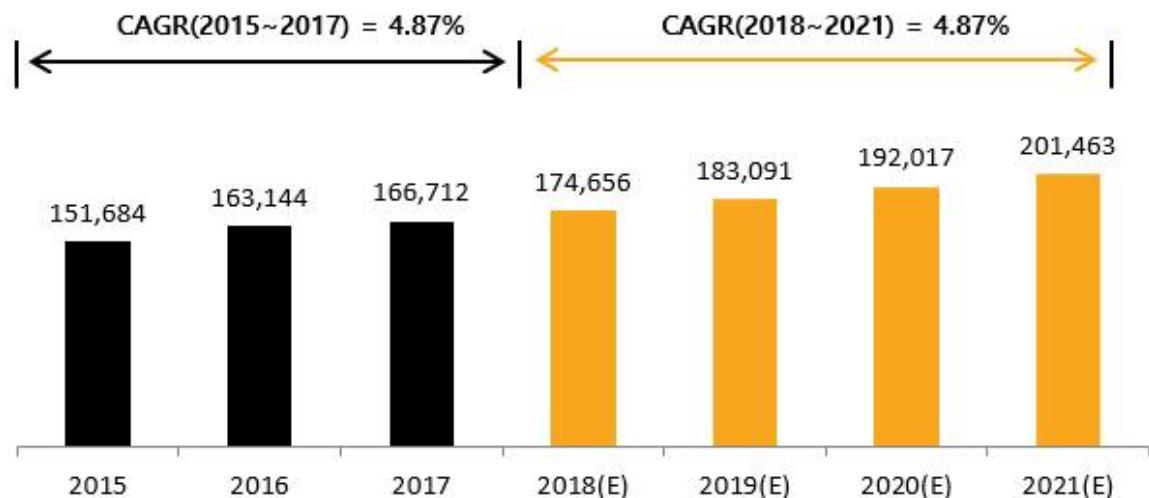

세계 시장에서 국내 시장이 차지하는 점유율(2017년 기준 24.14%)을 적용하여 추정한 결과 국내 반도체 패키징 시장은 2017년 16조 6,712억 원 규모이며, 이후 연평균 4.87%씩 증가하여 2022년에는 21조 1,427억 원에 달할 전망이다. 국내 반도체 패키징 및 조립 장비 시장은 시그네틱스, 하나마이크론, SFA 반도체, 앰코테크놀로지코리아, ASE코리아, 에이티세미콘, 윈팩 등이 참여하고 있다.

그림 6. 국내 반도체 패키징 시장 규모 (단위: 억 원)

\*출처: Technavio(2018), NICE평가정보(주) 재구성

### III. 기술분석

#### 첨단 신규 패키지 기술력을 보유한 시그네틱스

시그네틱스는 첨단 신규 패키지 제품인 플립칩 기술력을 보유하여 고부가가치 High-End 비메모리 반도체 제품 확대를 통해 최대 성장하고 있다.

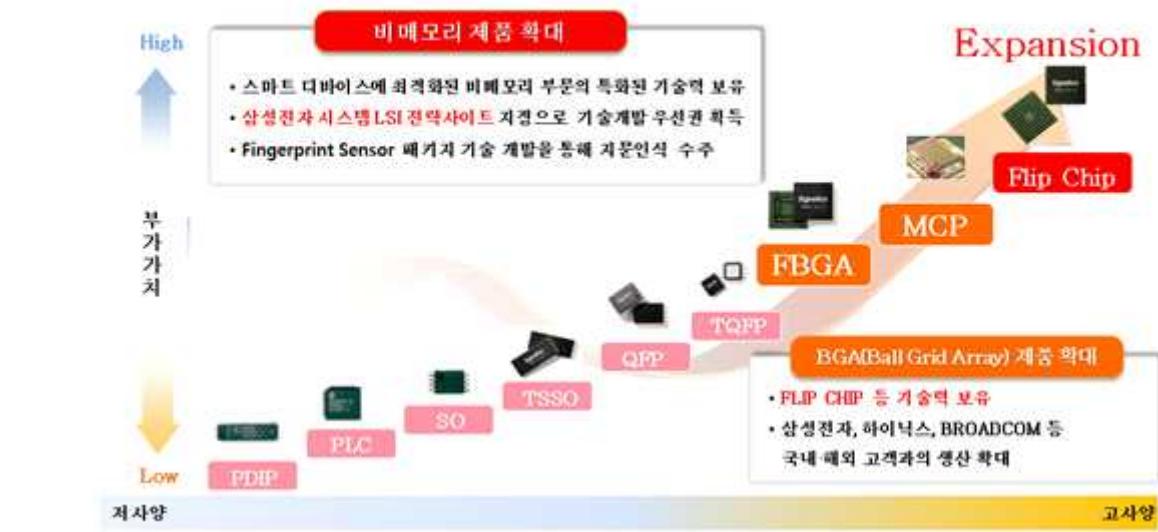

##### ■ 기술 포트폴리오

동사는 시장변화에 따라, 수익성이 낮고, 시장점유율이 떠조하는 PDIP/SOIC 제품에서 고부가가치의 제품으로 주요제품을 바꾸고 있다. 특히, 동사는 독자개발 및 특허를 취득한 STBGA(Signetcs Tape BGA) 양산체제를 구축한 후, 브로드컴 등의 해외고객에 대한 수주 증대를 통하여 매출 및 이익 증대와 고객 다변화를 하였다. 매년 꾸준하게 성장하는 CSP(Chip Scale Packaging) 계열인 FBGA 제품과 eMCP(embedded Multi Chip Package) 제품뿐만 아니라 첨단 신규 패키지 제품인 플립칩 라인을 증설 및 가동하여 매출 증대를 하고 있다. 또한, 공정능력을 향상하기 위해 지문인식 센서 제품을 지속적으로 개발하여 질적 성장에 주력하고 있다.

그림 7. 시그네틱스의 기술 포트폴리오

##### 고부가 가치 High-end 제품확대를 통한 최대 성장

\*출처: 분기보고서(2020), NICE평가정보(주) 재구성

동사는 지문인식 센서 패키지 기술개발을 통하여 매출을 확대하였고, 고부가가치 프리미엄 반도체 패키징 타입인 Recon 플립칩을 개발 및 지속 투자하여 양산하고 있다. 최근에는 전자기기들의 경량화, 다기능화에 따른 반도체 패키지의 SIP, Large Body, Fine pitch 등 새로운 비즈니스 매출창출을 위해 투자 및 개발하고 있다. 또한, Advanced SIP Module 제품의 수요 증가로 개발 및 초기 양산 인프라를 확보하였다.

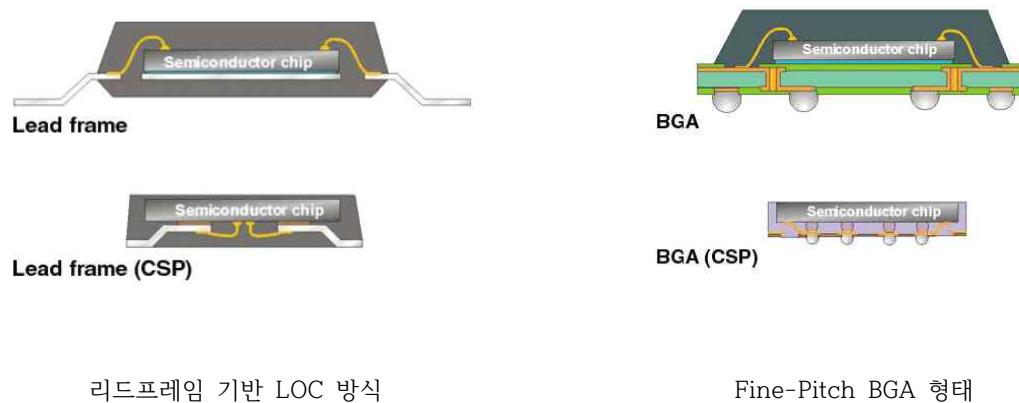

## ■ 반도체 패키지의 종류

반도체 패키징 기술은 초기의 삽입 실장형 패키지인 DIP, PGA 등에서 작고 전기적 성능이 우수한 표면 실장형의 SOP, QFP, BGA의 형태로 발전해 왔으며, 점차 경박단소화된 CSP의 외형에 내부 실장의 효율화를 위한 wafer 레벨 패키징과 적층 실장을 적용한 MCM, SiP 등으로 진화하고 있다. 전통적인 패키징 기술의 발전은 실장방식, 접속 단자의 수, 배치 방향, 간격 등 완성품의 외형상 변화로 설명될 수 있으며, 삽입실장형 패키징에서 표면 실장형으로 발전하여 최종적으로 CSP 혹은 FBGA로 표현되는 미세 단자 간격을 가지는 표실장형 패키징의 단계에 있다. 최근의 패키징 기술은 완성품의 외형을 CSP 등 전통적인 패키징 규격과 동일하게 유지하지만, 내부적으로는 플립칩 실장, wafer 레벨 패키징, 멀티칩 패키징, 3차원 적층 구조 등 동일 부피 및 면적 내에서 집적으로 효율성을 높일 수 있는 방향으로 변화하고 있다.

표 9. 최신 반도체 패키지의 종류

| 구분                            | 특징                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WL<br>(Wafer -Level)-CSP      | <ul style="list-style-type: none"><li>- Wafer 상태에서 칩을 절단하지 않고, 전면에 범프 배선구조를 미리 형성한 후 접속 단자 이외의 부분을 수지로 밀봉하여 완성하는 CSP 규격의 패키징 방식을 의미하여, 휴대용 디지털 가전 등의 초소형 소자를 위해 사용되는 첨단 패키징 기술임.</li><li>- WLCSP는 범프를 이용해 배선과 칩 고정을 하기 때문에 자연스럽게 플립칩 본딩 공정을 사용하나, 일반적인 CSP와 달리 칩과 PCB 사이에서 배선 밀도를 낮추어주는 인터포저를 사용하지 않고 칩 전면에 PCB 접속용 단자를 형성하는 방식임.</li></ul> |

| MCP<br>(Multi Chip Packaging) | <ul style="list-style-type: none"><li>- 기존의 단일칩 패키징(SCM)의 궁극적인 한계를 극복하기 위한 방식으로, 기존에 PCB에 패키지 형태로 각각 배치되던 다수의 칩들을 하나의 패키지 내에 실장 및 배선하여, 저전력, 고집적, 낮은 신호 손실 등의 장점을 얻기 위한 기술의 총칭임.</li><li>- MCP는 복수의 칩을 하나의 패키지 내부에 2D 혹은 3D로 쌓은 구조이며, 내부적인 변화와 관계없이 외형은 일반적인 BGA, QFP 등의 규격에 맞춘 형태를 갖기 때문에 외관에서는 MCP인지 여부를 구별하기 어려운 경우가 많음.</li></ul>       |

| MCM<br>(Multi Chip Module)    | <ul style="list-style-type: none"><li>- MCP 방식 중 주로 칩을 2차원으로 배치하고 와이어 본딩으로 배선한 형태를 가리키며, 특히 다수의 집적회로뿐 아니라 이전에 기판에 따로 배치되던 수동소자를 패키지 내부에 함께 실장하는 기술을 의미함.</li></ul>                                                                                                                                                                          |

| PoP<br>(Package on Package)   | <ul style="list-style-type: none"><li>- 여러 개의 단층 서브 패키지를 BGA 등의 전면 단자 형태로 구현하고, 순차적으로 적층하여 구현하는 가장 기초적인 3차원 패키징 기술로서, 기존의 패키징 기술을 재사용하기 때문에 개발 기간이 짧고 시장 대응성이 좋은 장점이 있음.</li></ul>                                                                                                                                                          |

| SiP<br>(System in Package)    | <ul style="list-style-type: none"><li>- MCP의 궁극적인 단계로서 용어 자체는 기존에 개별적으로 구현되어 PCB에 연결되었던 다수의 칩을 하나의 패키지에 실장한다는 뜻이지만, 일반적으로는 2차원 멀티칩 실장방식인 MCM과 구별되어 패키지 내에서 여러 칩을 3차원적으로 적층하는 방식을 의미함.</li></ul>                                                                                                                                             |

| TSV<br>(Thru-Silicon Via)     | <ul style="list-style-type: none"><li>- TSV는 기존의 본딩 와이어나 칩의 상부에 형성하던 범프 전극과 달리, 실리콘 wafer 자체에 구멍을 뚫고 구리 등 금속으로 내부를 메워, 칩의 반대 면에 배선하여 전극을 형성하는 방식으로, 칩 간 직접 접속을 통한 고밀도 3차원 적층 패키지 구현에 핵심적인 기술임.</li></ul>                                                                                                                                    |

\*출처: 분기보고서(2020), NICE평가정보(주) 재구성

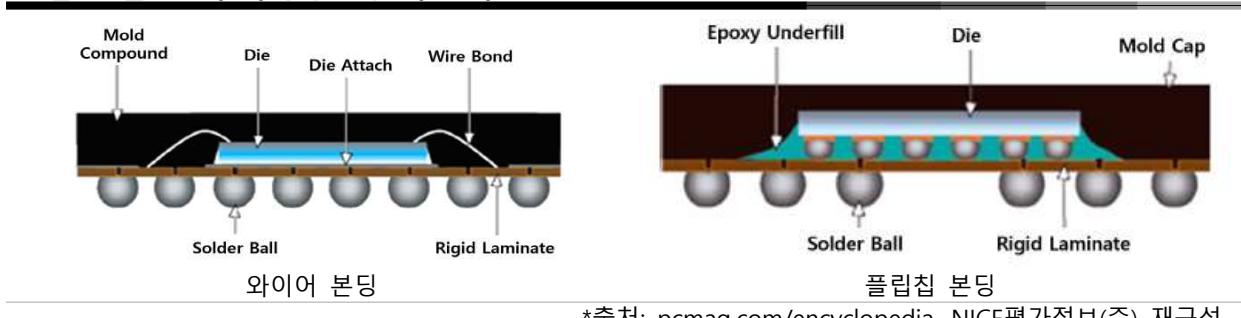

## ■ 플립칩 기술

플립칩 본딩 공정은 칩을 뒤집어서 기판 및 메인보드에 직접 실장하는 방식을 말하며, 이때 전기적인 배선이 칩의 전면 전극을 통해 이루어지기 때문에, 기존의 와이어 본딩 방식의 패키지에 비해 크기가 매우 작고 배선 수가 많아질수록 배선을 하나씩 연결하는 와이어 본딩에 비해 공정비용이 크게 절감되는 효과가 있다. 플립칩은 전통적인 반도체 패키징 방식과 구조가 상이한 만큼 조립 공정 역시 크게 다르며, wafer 상태에서 칩의 표면에 도체물질로 5~10 $\mu\text{m}$  크기의 미세 접속단자인 범프(Bump)를 형성한 후, 범프가 형성된 면을 뒤집어 기판에 직접 접합하여 칩의 전기적 연결, 물리적 결합, 열 방출로를 동시에 확보한다.

그림 8. 플립칩과 와이어 본딩 기술 비교

\*출처: pcmag.com/encyclopedia, NICE평가정보(주) 재구성

플립칩 본딩 공정의 범프는 크게 솔더(Solder) 범프와 금 스터드(Au Stud) 범프로 구분되며, 이 중 대부분을 차지하는 솔더 범프의 경우 범프를 형성하기 전에 먼저 칩의 전극을 형성할 부분 위에 UBM(Under Bump Metalization) 층을 형성하는 과정을 거친다. UBM이란, 대부분 반도체 칩의 본딩 패드가 와이어 본딩을 위한 알루미늄, 구리로 구성되어 있어 공기에 노출되면 자연 산화막이 발생하여 절연성을 띠게 되므로, 약품으로 이를 제거하고 그 위에 솔더 범프를 접합할 수 있는 얇은 다층 금속층을 도포하는 과정을 말한다. 솔더 범프는 진공증착(Evaporation), 전해도금(Electroplating), 또는 스크린 프린팅(Screen Printing) 방식으로 각 방식에 맞는 특정한 UBM 층을 형성한 후 그 위에 도포하며, 형성된 솔더 범프는 리플로우 공정을 거치면서 솔더 자체의 표면장력에 의하여 볼모양의 전극을 형성한다.

## ■ 패키징 기술의 발전 방향

최근 반도체 기술의 발전과 함께 칩의 단위 면적당 단자 수는 증가하는 반면, 동작의 고속화에 따라 신호 감쇄의 원인이 되는 배선 선로의 길이는 제한되는 등, 패키징 기술의 고도화에 대한 요구가 증가하고 있으며, 이에 따라 소형의 고집적 패키징 기술이 주목을 받고 있다. 패키징의 발전은 삽입 실장형에서 표면 실장형으로, 외형상 접속단자 수 증가와 미세 단자화, 전면 단자의 채용 등 경박단소화와 고밀도화의 방향으로 진행되어, 현재 CSP로 대표되는 미세 단자 표면실장형에 이르렀으며, 점차 내부 칩 실장의 효율성을 높인 wafer 텐셀 패키징, MCP, SiP 등의 형태로 변화하고 있다. 전통적인 패키징 방식인 리드프레임과 와이어 본딩은 공통적으로 칩의 측면에서 배선하는 방식으로 밀도가 낮고 배선이 길기 때문에, 점차 범프를 이용하여 플립칩 본딩을 하고, 다시 적층 회로 기판의 솔더볼 전면 단자로 연결하여 전체 배선을 수직 방향으로 짧게 하는 것이 전반적인 흐름이다.

CSP는 패키지의 외형명이 아닌, 최종 완성품의 크기가 내장하는 반도체 칩과 같거나, 최대 120%를 넘지 않는 초소형 패키징을 총칭하는 것으로 단일칩 패키징 중 가장 발전된 형태의 기술을 의미한다. CSP 기술은 리드프레임과 적층 회로기판을 이용하는 두 가지 패키징 방식에서 모두 구현이 가능하며, 이 중 리드프레임을 기반으로 하는 LOC(Lead On Chip) 방식은 칩과 거의 같은 크기의 리드프레임을 이용하여 칩의 중앙부에서 미세 와이어 본딩 기술로 배선하며, 주로 메모리 칩 등에 사용된다. 일반적으로 사용되는 CSP 패키지는 많은 수의 접속 단자 수를 확보하기 위해 주로 플립칩 본딩을 사용하는 발전된 BGA 형태로 구현되며, 이때 단자 간격은 일반적인 BGA에 비해 축소되어 0.8mm 이하가 되며, 패키지의 외형명은 FBGA로 분류된다.

**그림 9. 플립칩과 와이어 본딩 기술 비교**

리드프레임 기반 LOC 방식

Fine-Pitch BGA 형태

\*출처: Encyclopedia, NICE평가정보(주) 재구성

## ■ 시그네틱스의 생산체계 전략

### ▶▶ Fine Pitch Wire Bonder 구비

고집접화, 고용량화라는 반도체 시장변화에 따라 시장의 주력 제품이 기존 PDIP / SOIC 등 제품에서 BGA / FBGA / 플립칩/ 고단 Stacked 등으로 변화함에 따라, 기존 Wire Bonder로는 시장의 요구를 따라갈 수 없어 동사는 고성능 및 Fine Pitch에 적합한 Iconn 등의 Wire Bonder 설비를 교체하여 시장변화에 대응하고 있다.

### ▶▶ 12인치 wafer 생산 가능한 설비 구축

반도체 종합회사들이 수율 향상을 위하여, wafer 크기를 12인치로 증대함에 따라, Back Grinding, Die Bonder 등 12인치 wafer를 생산할 수 있는 설비를 구축함으로써, 수주향상에 기여하고 있다.

표 10. 동사의 각 기술에 따른 경쟁력 평가

| 기술명                                              | 경쟁력 평가                                                                                                                                     |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Low k wafer Saw<br>(60nm, 45nm, 32nm)            | 저유전체(Low k) 물질 사용<br>- 첨단 디바이스의 회로 배선 폭을 줄이고 속도를 빠르게 하면서 상호 간섭을 저감<br>- 기존의 유전체 물질보다 열적 안정성 우수                                             |

| wafer Thinning<br>(50um, 40um, 30um)             | wafer의 두께를 얇게 Grinding 할 수 있는 기술<br>- 반도체 부품의 경박단소화 및 Multi Die Stack을 통한 고성능/고집적 기술 확보                                                    |

| Stacked PKG<br>(Die Overhang)                    | Low Profile Package 구현<br>- Die Stack 공정 중 발생 되는 Die Overhang에 의한 Bounce 극복을 위한 기술                                                         |

| Fine Wire Bonding                                | 정밀 Wire Bonding 공정 기술<br>- 디바이스의 회로 배선 폭이 줄어들면서 전기적 연결을 위한 Bond Pad Pitch가 매우 좁아짐으로 인해 Wire Bonding 공정에서 요구되는 기술로 고객의 생산성 증대               |

| Cu & CuPd Wire                                   | 금실(Gold Wire) → 구리 실(Copper Wire)<br>- 금실(gold wire)을 대신하여 구리 실(copper wire)을 사용하기 위한 기술로 Package 단가 경쟁력을 통해 Market 선점의 이점 보유              |

| Fine Solder Ball<br>Pitch &<br>Small Ball Attach | 동일 Package내 I/O 수의 증가를 가능할 수 있게 하는 기술<br>- Solder Ball Pitch와 작은 Solder Ball 취급을 지원<br>- Package Size 축소를 통한 생산성 향상 및 원가 절감                |

| Flip Chip Bonding                                | 반도체 칩을 회로기판에 부착하는 본딩 기술<br>- 현재의 Wire 또는 TAB Bonding보다 접속 배선의 길이가 짧음.<br>- 배선 Inductance가 작고 고속 대응 Package에 적합                             |

| Cu Pillar Bump                                   | 차세대 Flip Chip Bumping 기술<br>- 도전성이 뛰어난 Cu를 이용 → Electromigration에 대응<br>- 미세 Bump Pitch 구현이 가능하여 I/O의 선간 미세 배열 (80~130 um)을 통한 IC 밀집도를 극대화 |

| Molded Under Fill                                | 몰딩(Molding)이라는 범용 기술을 사용<br>- Low Cost Marketing을 통하여 높은 시장 점유 가능                                                                          |

\*출처: 분기보고서(2020), NICE평가정보(주) 재구성

## ■ 지식재산권 현황

2010년 이후에 동사가 등록한 지식재산권 현황은 [표 11]과 같다.

표 11. 등록된 특허 현황

| 출원국  | 등록일          | 발명의 명칭                                    |

|------|--------------|-------------------------------------------|

| 대한민국 | 2020. 09. 29 | 지문인식 센서 패키지                               |

| 대한민국 | 2019. 02. 07 | 지문인식 센서 패키지                               |

| 대한민국 | 2017. 12. 08 | 지문인식 센서 패키지 및 그 패키지를 포함하는 PCB 스트립 패키지 구조체 |

| 대한민국 | 2018. 05. 28 | 칩 몰딩 장치                                   |

| 대한민국 | 2018. 03. 29 | 칩 몰딩 장치                                   |

| 대한민국 | 2017. 12. 08 | 지문인식 센서 패키지 및 그 패키지를 포함하는 PCB 스트립 패키지 구조체 |

| 대한민국 | 2017. 12. 08 | 스테이션 블록                                   |

| 대한민국 | 2017. 09. 25 | 몰딩 공정용 피크                                 |

\*출처: 특허정보넷(KIPRIS), NICE평가정보(주) 재구성

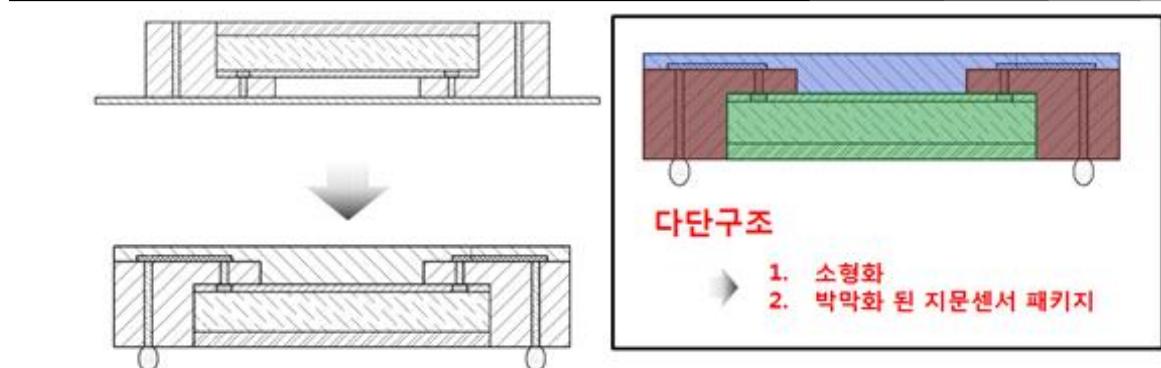

## ▶▶ 지문센서 패키지 원천기술 확보 노력

지문센싱용 패키지는 지문정보 획득의 신뢰성과 감도를 유지하면서 동시에 전체적인 크기와 높이를 줄일 것이 요구되고 있다. 지문인식 기술은 사용자의 지문을 인식함으로써 기기의 등록 및 인증 절차를 거치게 하여 각종 보안사고를 예방하는데 주로 이용되는 기술이며, 특히, 개인 및 조직의 네트워크 방어, 각종 콘텐츠와 데이터의 보호, 안전한 액세스 제어 등에 적용되는 기술이다. 지문센서는 사람의 손가락의 지문정보를 획득하며, 지문정보는 광학식, 정전 용량이나 전기 전도를 감지하는 반도체 소자 방식, 초음파 방식, 열 감지 방식 등을 이용하여 획득된다.

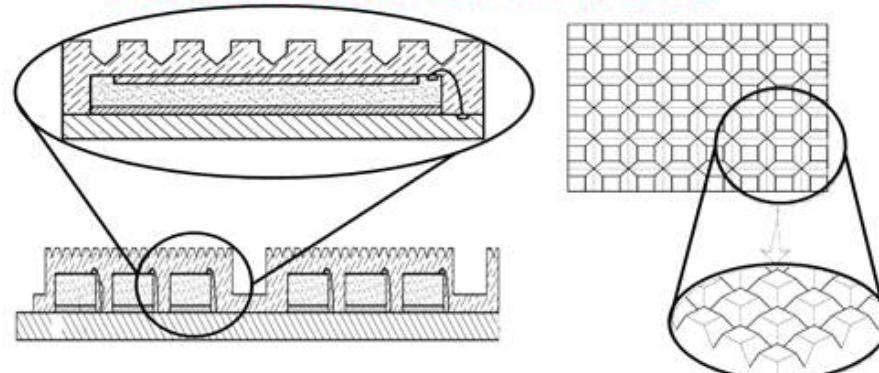

그림 10. 지문센서 패키지 및 그 제조 방법(10-2016-0004396)

\*출처: 지문센서 패키지 및 그 제조 방법(10-2016-0004396), NICE평가정보 재가공

[그림 10]은 지문센서 패키지 및 그 제조방법에 관한 것으로, 시그네틱스는 다단구조를 가지는 기판 내에 수용하여 지문정보 획득의 신뢰성과 감도를 유지함과 동시에 소형화, 박막화된 지문센서 패지지 제공하는 기술을 보유하고 있다. 또한, [그림 11]의 지문인식 센서 패키지 및 그 패키지를 포함하는 PCB 스트립 패키지 구조체에서의 지문인식 센서를 덮는 몰딩 부재의 상면상에 굴곡들이 형성됨으로써, 지문인식 센서 패키지의 구부림(Bending) 및 유연성(Flexibility)의 향상 기술을 보유하고 있다.

그림 11. 지문센서 패키지 및 그 제조 방법(10-2016-0004396)

### 구부림(Bending) 및 유연성(Flexibility)의 향상

\*출처: 지PCB 스트립 패키지 구조체(10-1809004), NICE평가정보 재가공

## ■ SWOT 분석

그림 12. 동사 SWOT 분석

\*출처: NICE평가정보

### ▶▶ (Strong Point) 고부가가치 프리미엄 반도체 패키지 기술 보유 및 지속적인 투자

CSP 계열인 FBGA 제품과 eMCP 제품뿐만 아니라 첨단 신규 패키지 제품인 플립칩 라인을 증설 및 가동하여 매출 증대를 하고 있다. 또한, 지문인식 센서 패키지를 지속적으로 개발하여 질적 성장에 주력하고 있다.

### ▶▶ (Opportunity Point) 4차 산업 혁명에 따른 시스템 반도체 시장확대

4차 산업 혁명으로 IoT, 자율주행 자동차, 인공지능 반도체 분야에 대한 시스템 반도체 수요가 크게 확대될 것으로 예상됨에 따라 자연스럽게 반도체 패키징 회사들의 성장이 기대된다.

### ▶▶ (Weakness Point) 높은 연구개발 비용과 낮은 인력수급 유동성

패키징 기술이 고집적, 소형화로 변모하면서 패키징 기술의 복잡도가 높아지고 있어 개발 인력의 높은 전문성이 요구된다. 한편, 중소기업으로 고급 인력수급의 유동성이 다소 낮은 편이며, 고가의 장비 투자가 불가피하여 연구개발비가 큰 편에 속해 초소형화, 초박형화를 구현하는 제조 및 생산기술의 확보, 프로세스의 혁신, 연구개발 등을 통해 경쟁력과 부가가치를 더욱 높여야 할 필요가 있다.

### ▶▶ (Threat Point) Covid-19에 따른 중국 시장의 불확실성

Covid-19에 의한 반도체 시장 성장 위축이 선진 반도체 패키지 업체들과의 기술 격차를 가속화 시킬 위험이 있다. 국내 반도체 장비산업은 삼성전자, SK하이닉스 등 대형 메모리 반도체 업체와 함께 성장하였기 때문에 고부가가치 반도체 패키지에서의 시장을 확대하기 위해서는 다양한 세계적인 시스템 반도체 업체들로의 고객 다변화가 필요하다.

## IV. 재무분석

### 종합 반도체 패키징 전문기업

동사는 1966년도에 전자장치 및 동 부속품의 제작과 판매 등을 목적으로 설립된 후, 국내외 유수 전자업체와 긴밀하고 장기적인 협력 관계를 유지하여 선도적인 반도체 공급업체로 성장하였다. 동사는 세계 반도체 패키지 시장에서 요구하는 최첨단 패키지 기술을 보유하고 있으며, 지속적인 연구 개발 및 설비투자를 통해 기술경쟁력을 유지하여 2019년 기준 국내 반도체 패키징 시장에서의 동사 시장 점유율은 6.6%를 차지하였다.

#### ■ 글로벌 TOP 반도체 후공정 및 테스트 사업을 영위

동사의 사업부문은 연결기준으로 크게 메모리와 비메모리 반도체 제조로 구성되어 있으며, 2019년 결산 비메모리 반도체 사업부문은 1,264억 원(총매출의 57.8%)으로 메모리 반도체 사업부문 매출 924억 원(총매출의 42.2%)을 상회하고 있다.

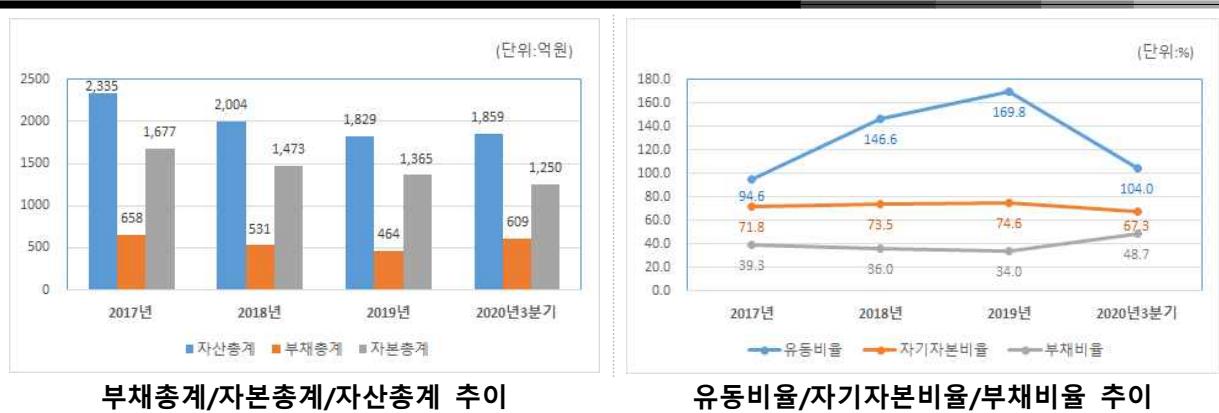

그림 13. 동사 연간 및 3분기 요약 포괄손익계산서 분석

\*출처: 동사 사업보고서(2019), 분기보고서(2020)

그림 14. 동사 연간 및 3분기 요약 재무상태표 분석

\*출처: 동사 사업보고서(2019), 분기보고서(2020)

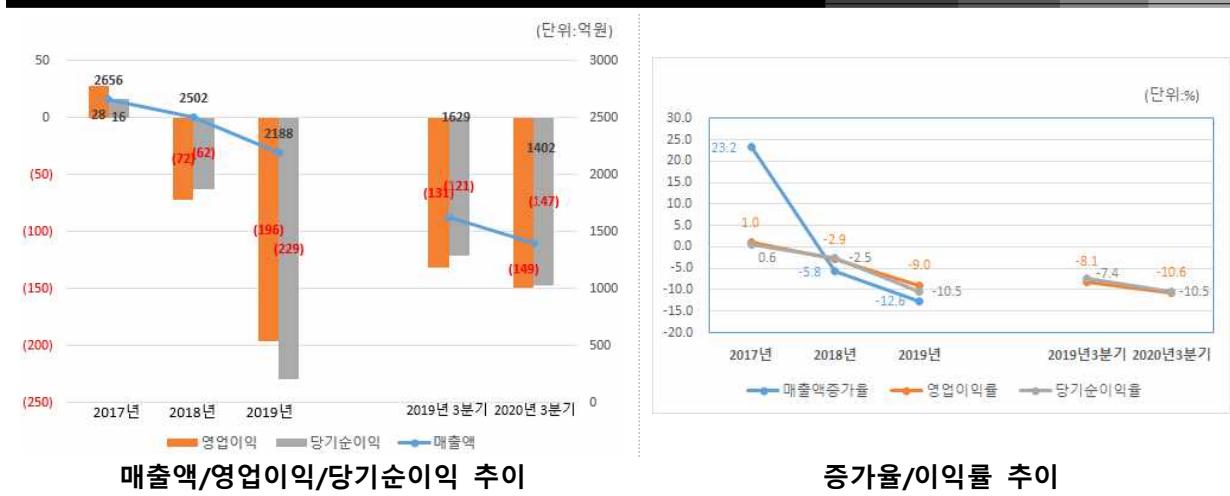

## ■ 매출액 감소세 및 수익성 적자 지속

삼성전자, SK하이닉스, Broadcom 등의 반도체 출하량 감소에 따른 관련 패키징 수요 부진으로 2019년 결산 연결기준 매출은 전년 대비 12.6% 감소한 2,188억 원을 기록하였다.

동사의 매출액은 2017년 2,656억 원(+23.2% YoY), 2018년 2,502억 원(-5.8% YoY), 2019년 2,188억 원(-12.6% YoY)을 기록하며 매출액 감소 추세를 보였다.

동사의 매출원가율은 2018년 99.3%, 2019년 103.1%로 원가율이 상승한 가운데 판관비용 부담 또한 확대되면서 매출액영업이익률 2018년 -2.9%, 2019년 -9.0%, 매출액순이익률 2018년 -2.5%, 2019년 -10.5%로 수익성이 하락한 모습을 보였으며, 손실 폭이 확대되었다.

## ■ 2020년 3분기 매출액 감소 및 순손실 확대

주요 매출처향 수주 지연의 영향으로 2020년 3분기 누적 매출액은 전년 동기 대비 14.0% 감소한 1,402억 원을 기록하였다. 외형 축소의 영향으로 원가율이 상승한 가운데 판관비용 부담 또한 가중되어 수익성이 전년 동기 대비 저하되었으며, 매출액영업이익률 -10.6%, 매출액순이익률은 -10.5%로 적자 수익구조를 지속 및 순손실 폭이 확대되었다.

주요 재무안정성 지표는 순손실 지속으로 자기자본이 축소된 가운데 차입금 증가로 부채규모가 확대되어 부채비율 48.7%, 자기자본비율 67.3%, 유동비율 104.0%를 기록함에 따라 2019년 결산 대비 안정성 지표는 저하되었으나, 보유 유형자산 등을 감안한 재무부담은 무난한 수준을 유지하고 있다.

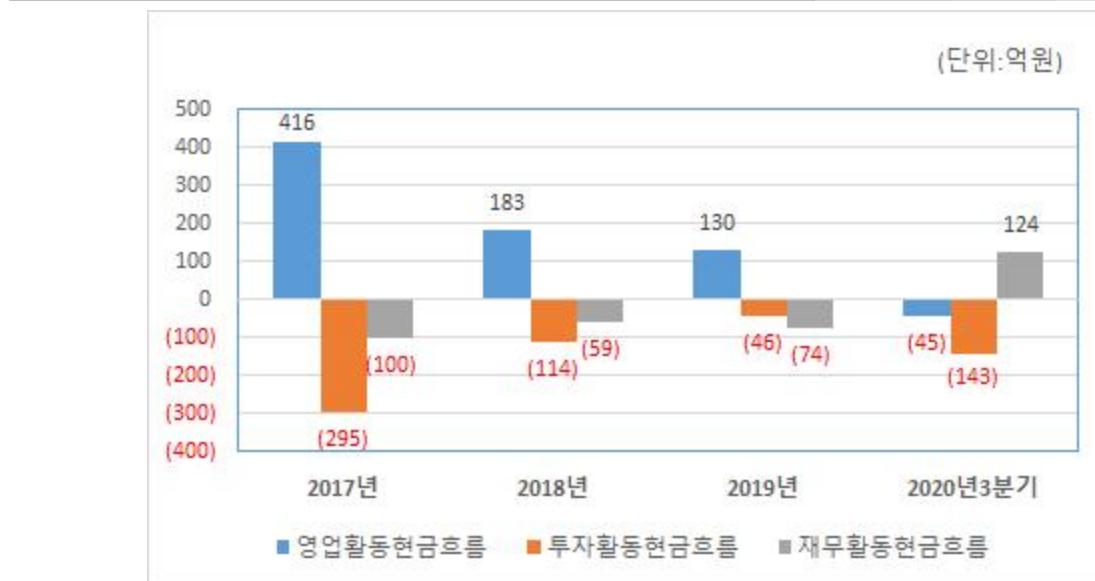

## ■ 무난한 자금흐름 유지

2019년 결산 영업활동현금흐름은 순손실 폭 확대에도 불구하고 유형자산감가상각비 등 실질적인 현금 유출이 없는 비용 등의 가산과 재고자산 감소에 힘입어 130억 원을 기록하며 흑자 상태를 유지하였고, 이를 통해 건물, 기계장치 등 유형자산 취득에 소요되는 자금을 충당하고 차입금을 일부 상환하여 무난한 자금흐름을 유지하였다.

그림 15. 동사 현금흐름의 변화

\*출처: 동사 사업보고서(2019) 분기보고서(2020)

## V. 주요 변동사항 및 향후 전망

### IoT, 자율주행, 인공지능 등의 4차 산업 혁명에 따른 시장확대 및 성장 기대

시그네틱스는 기존의 반도체 패키지 라인업에 플립칩 등의 첨단 패키지 기술력을 확보하여 국내 및 세계 점유율을 확장해가고 있으며, 지문인식 센서용 패키지 분야로도 사업 부문을 확장하여 매출 증대가 기대된다.

#### ■ 고부가가치 제품으로의 성장 포트폴리오 수립 전략에 따른 경쟁력 강화

동사는 수익성이 낮고, 시장점유율이 떠조하는 PDIP/SOIC 제품에서 고부가가치의 제품으로 주요제품을 바꾸고 있다. 매년 꾸준하게 성장하는 CSP 계열인 FBGA 제품과 eMCP 제품뿐만 아니라 첨단 신규 패키지 제품인 플립칩 라인을 증설 및 가동하여 매출 증대를 하고 있다. 또한, 동사는 지문인식 센서 패키지 기술개발을 통하여 매출을 확대하였고, 고부가가치 프리미엄 반도체 패키징 타입인 Recon 플립칩을 개발 및 지속 투자하여 양산하고 있다. 최근에는 전자 기기들의 경량화, 다기능화에 따른 반도체 패키지의 SiP, Large Body, Fine pitch 등 새로운 비즈니스 매출창출을 위한 LAB 기술을 투자 및 개발하고 있으며, Advanced SiP Module 제품의 수요 증가로 개발 및 초기 양산 인프라를 확보하였다.

#### ■ 다양한 고객과 전략적 파트너쉽

국내외 유수 전자업체와 긴밀하고 장기적인 협력 관계를 유지하여 선도적인 반도체 공급업체로서 자리매김은 물론, 본사 및 미국 캘리포니아 프리몬트 지사와 어바인 기술 및 디자인 센터와 연계하여 전통적 고객과 공급자 관계를 넘어선 전략적 파트너로 국내외 반도체 패키징 발전에 선도적인 역할을 하고 있다. 또한, 고객 다변화를 위한 지속적인 노력을 하고 있다.

#### ■ 생산체제 전략

Fine Pitch Wire Bonder 설비 교체 및 12인치 wafer 생산 가능한 설비 구축 등과 같이 지속적인 투자를 통한 첨단 신규 패키지 기술에 대한 생산체제를 구축함으로써 수주향상과 시장변화에 대응하고 있다.

## ■ 증권사 투자의견

| 작성기관                                                                | 투자의견 | 목표주가 | 작성일 |

|---------------------------------------------------------------------|------|------|-----|

|                                                                     |      |      |     |

| <ul style="list-style-type: none"><li>최근 6개월 이내 발간 보고서 없음</li></ul> |      |      |     |

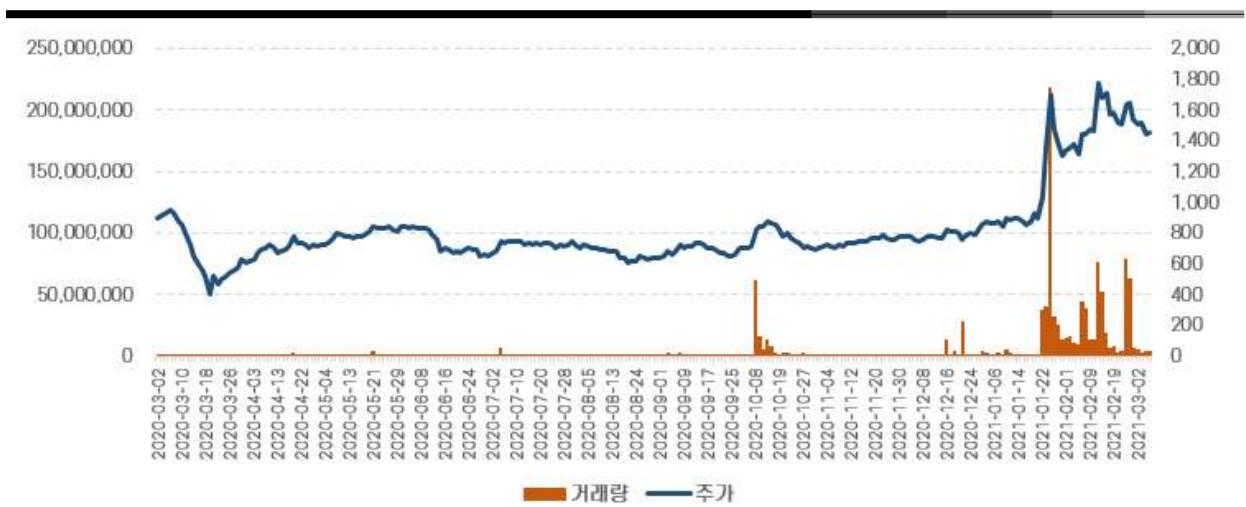

## ■ 시장정보(주가 및 거래량)

\*출처: Kisvalue(2021.03)